## Mastering DSP in VHDL

Fixed point arithmetic

complex VHDL design using Digital signal processing

- Digital filtering

- **C++**

- Matlab

- Signal Theory

## Mastering DSP in VHDL

**Start Learning VHDL using FPGA**

Write to: info@surf-vhdl.com

- continuous-time signal

- discrete-time signal

- Time domain and Frequency domain representation

- Function  $\delta(n)$  and u(n)

- Analog to Digital and Digital to Analog Conversion

- Quantization error, SRN, SINAD

- Introduction to Digital Filter Design

- Example of Mobile Average Filter

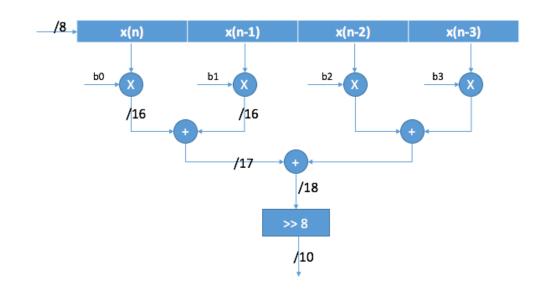

- FIR general architecture

- Frequency response

- Impulse response

- Step response

- MATLAB/C++ implementation

- Symmetric FIR

- Antisymmetric FIR

- **™** Half-Band FIR

- Introduction to Fixed point arithmetic

- Floating point -> Fixed point

- Fixed point representation

- Add, Sub, Mult, Acc

Filter synthesis using Matlab/Octave

Filter design example using the Matlab Remez function to synthesize a digital filter

Fixed point verification Matlab/Octave/C++

- VHDL implementation of Mobile Average Filter

- VHDL implementation of classic FIR

- VHDL implementation of a symmetric FIR

- VHDL implementation of an antisymmetric FIR

- Introduction to multi-rate filter

- Interpolation

- FIR Interpolator

- Decimation

- FIR Decimation

- Fractional interpolation/Decimation